# ISA-L® UPDATE & USERCASE SHARING

SPDK China Summit 2018

Xiaodong Liu (Xiaodong.liu@intel.com)

Chunyang Hui (Chunyang.hui@intel.com)

### Legal Disclaimer

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration.

No computer system can be absolutely secure.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/benchmarks">http://www.intel.com/benchmarks</a>.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <a href="http://www.intel.com/benchmarks">http://www.intel.com/benchmarks</a>.

Benchmark results were obtained prior to implementation of recent software patches and firmware updates intended to address exploits referred to as "Spectre" and "Meltdown." Implementation of these updates may make these results inapplicable to your device or system.

Intel® Advanced Vector Extensions (Intel® AVX)\* provides higher throughput to certain processor operations. Due to varying processor power characteristics, utilizing AVX instructions may cause a) some parts to operate at less than the rated frequency and b) some parts with Intel® Turbo Boost Technology 2.0 to not achieve any or maximum turbo frequencies. Performance varies depending on hardware, software, and system configuration and you can learn more at <a href="http://www.intel.com/go/turbo">http://www.intel.com/go/turbo</a>.

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

© 2018 Intel Corporation.

# ☐ Features Update & Usercase Sharing

- Encryption

- Stitching

- CRC64

- Compression

- Multi-buffer Hash

- ☐ State of the Project

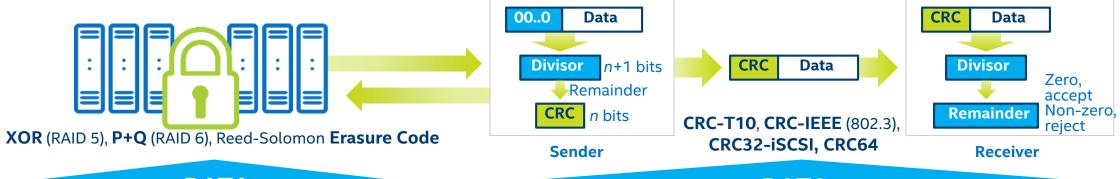

### Intel® ISA-L Functions

DATA PROTECTION

DATA INTEGRITY

#### **PERFORMANCE OPTIMIZING**

# CRYPTOGRAPHIC HASHING

Multi-Buffer: SHA-1, SHA-256, SHA-512, MD5

Multi-Hash: SHA1, SHA1+Murmur

## COMPRESSION "DEFLATE"

IGZIP: Faster DEFLATE (zlib)

Compression & Decompression

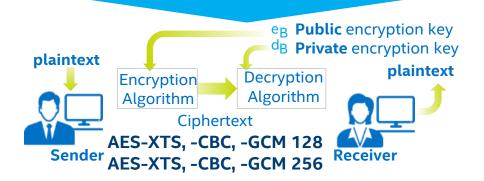

#### **ENCRYPTION**

# **ENCRYPTION**

#### Encryption Cycle/Byte Performance on the

#### Intel® Xeon® Processor Scalable Family

| (cache cold cycle/byte) | Ir                                              | ntel® Xeon® Platinum 8180 Proces             | ssor @ 2.5 GHz 1 Socket                     |                                              |

|-------------------------|-------------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|

| ISA-L Function          | ISA-L                                           | ISA-L                                        |                                             | SL 1.0.2j                                    |

|                         | <b>Cycle/Byte Performance</b> (lower is better) | Single Core Throughput<br>(higher is better) | Cycle/Byte Performance<br>(lower is better) | Single Core Throughput<br>(higher is better) |

| AES-XTS 128             | 0.64                                            | 3.8 GB/s                                     | 0.64                                        | 3.8 GB/s                                     |

| AES-XTS 256             | 0.88                                            | 2.7 GB/s                                     | 0.89                                        | 2.7 GB/s                                     |

| AES-CBC 128<br>Decode   | 0.64                                            | 3.8 GB/s                                     | 0.64                                        | 3.8 GB/s                                     |

| AES-CBC 192<br>Decode   | 0.76                                            | 3.2 GB/s                                     | 0.76                                        | 3.2 GB/s                                     |

| AES-CBC 256<br>Decode   | 0.88                                            | 2.7 GB/s                                     | 0.88                                        | 2.7 GB/s                                     |

| AES-GCM 128             | 0.67                                            | 3.6 GB/s                                     | 1.58                                        | 1.5 GB/s                                     |

| AES-GCM 256             | 0.89                                            | 2.7 GB/s                                     | 1.83                                        | 1.3 GB/s                                     |

All results collected by Intel Corporation

AVX512 instructions

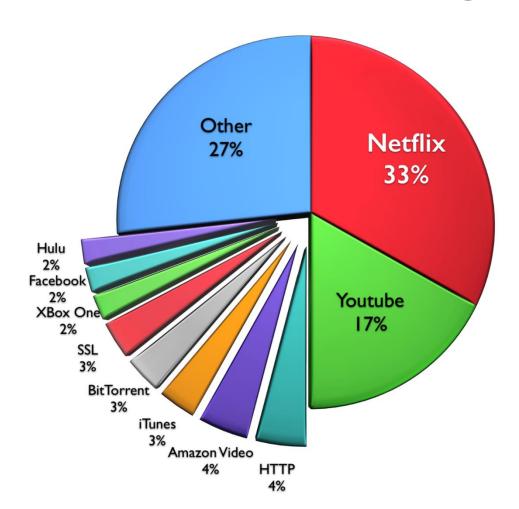

### Netflix & Intel: Background

#### North American Aggregate Internet Traffic

Sandvine 2016 Global Internet Phenomenon Report https://www.sandvine.com/trends/global-internet-phenomena

#### **Netflix pushes how many bits?**

Average of 35Tb/s all day, every day, and rising

#### And how do they do it?

- Built their own custom Content Delivery Network

- Vast majority of the library is served from boxes living in your local ISP/IXP

- Heterogeneous hardware, but all single socket, all FreeBSD based

#### How come?

- Saves vast amounts of backbone traffic

- Gives Netflix direct control at both ends of the wire

- Improves user experience

### The Challenge

#### **Design Goal:**

Upgrade to 100Gbps per Open Connect Appliance

#### **Curveball:**

Add encryption (HTTPS/TLS) for streaming video to safeguard user privacy, too

#### **Budget:**

Do it cost effectively

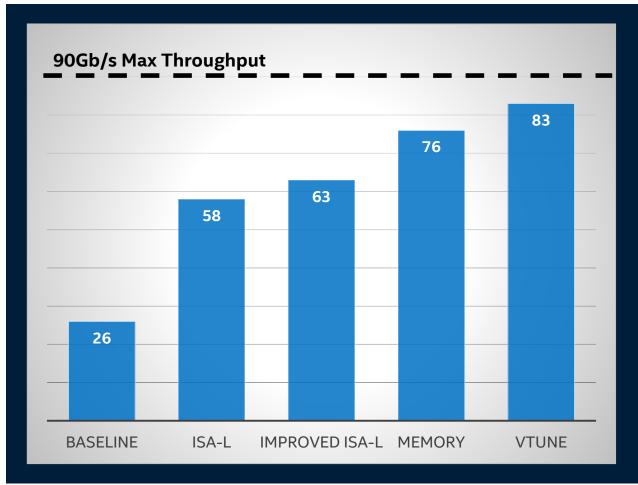

### Netflix & Intel: Before and After

#### **Started with OpenSSL**

Required compromises in their data path

#### Tried all the alternatives: BoringSSL, etc.

- ISA-L was the fastest on the market

- Long-lived connections, only in the data path

#### ISA-L was tweakable

- Asked for non-temporal instructions: eureka!

- Identified the bottleneck: memory bandwidth

- Tuned the hardware

- ... but it also fit the entire deployed infrastructure

#### **Netflix\* 2016 100G Flash OCA Performance**

# FUNCTIONS STITCHING

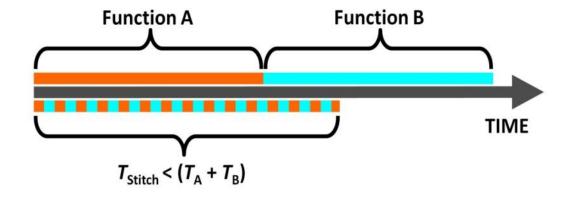

#### Definition:

A method to interleave instructions from pairs of functions to maximize execution efficiency of the cores.

#### Advantages:

- In turn allows the processor core to execute instructions from both algorithms at the same time, makes better use of the execution resources, and results in a lower total execution time.

- May also offer second-order benefits, such as only requiring data to be fetched from memory/caches once rather than twice.

**Figure 1. Stitching Two Functions**

#### Usercases

"We were able to run with the new T10PI calculate and move routines you created. The API works well for us, and so does the routine. With this routine, we improved performance (in our usage) from  $\sim$ 3.0 GB/s to  $\sim$ 5.1 GB/s!

-- Data from a famous storage solution company in US

# USING CRC64

### **CRC Update**

Definition: A Cyclic Redundancy Check (CRC) is the remainder, or residue, of binary division of a potentially long message, by a CRC polynomial. This technique is ubiquitously employed in communication and storage applications due to its effectiveness at detecting errors.

#### Types

- CRC16: T10 standard

- CRC32: IEEE standard, gzip standard (IEEE reflected), iSCSI

- CRC64: ECMA-182 standard (reflected/normal), ISO standard (reflected/normal) ...

#### ISA-L Specific

- Self defined polynomial supported

- 64 bit is as fast as 32 bit CRC

- Instruction level supported for CRC32 iSCSI

|                       | Intel® Xeon® Platinum 8180 Processor @ 2.5 GHz 1 Socket |                                              |  |

|-----------------------|---------------------------------------------------------|----------------------------------------------|--|

| ISA-L Function        | ISA-L                                                   |                                              |  |

|                       | <b>Cycle/Byte Performance</b> (lower is better)         | Single Core Throughput<br>(higher is better) |  |

| CRC16 T10             | 0.22                                                    | 11.0 GB/s                                    |  |

| CRC32 IEEE (802.3)    | 0.22                                                    | 11.1 GB/s                                    |  |

| CRC32 iSCSI           | 0.18                                                    | 13.8 GB/s                                    |  |

| CRC32 GZIP Reflective | 0.24                                                    | 10.3 GB/s                                    |  |

| CRC64 Normal          | 0.22                                                    | 11.0 GB/s                                    |  |

| CRC64 Reflective      | 0.19                                                    | 12.9 GB/s                                    |  |

\*\* ISA-L function uses AVX512 instructions

performance of Intel products, visit Intel Performance Benchmark Limitations (http://www.intel.com/performance/resources/benchmark\_limitations.htm).

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, compositively only on the performance tests and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including performance of that product when combined with other products. For more information go to http://www.intel.com/performance.

### CRC64 Usage Case

The Intel team helped this company by writing custom assemblers that worked with its generic polynomial implementation, which later was incorporated it into their software,

"The result of this was a reduction of 33% in the latency for the temp which has direct impact in the job performance. The performance of the iSCSI implementation of CRC also improved by 2.9x and it provided a 7.9x improvement in performance of CRC64."

-- data from a famous world wide software company

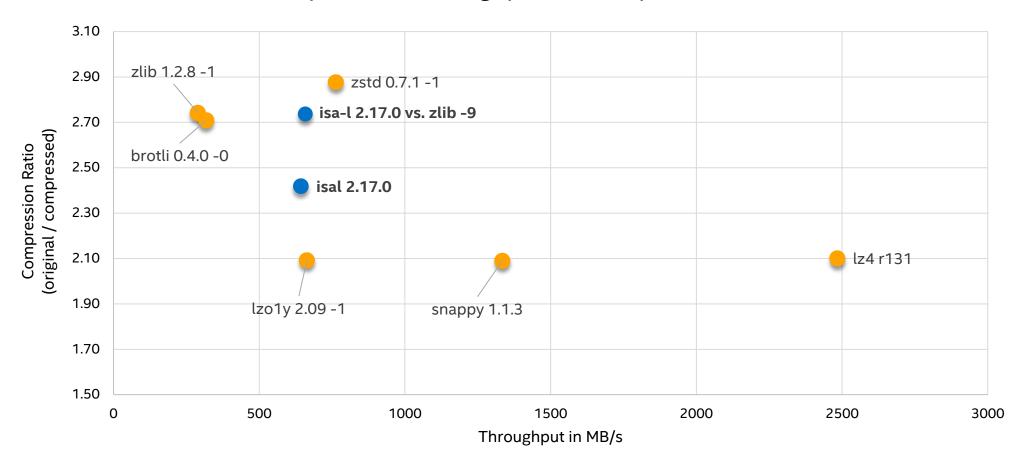

# COMPRESSION

#### **DEFLATE** (aka zlib, gzip, pkzip, etc)

- Lossless compression, ubiquitous adoption

- Web servers & clients, MS Windows, DirectX & Office, Android apps, png images, pdf files.

#### **Fast Compression**

Novel, fully zlib-compatible implementation:

- Level 0-3 optimized for throughput

- 5X greater throughput than zlib-1, equal to lz4 and lzo

- 6% better compression ratio than lz4 and lzo with same throughput

- semi-dynamic compression allows granular tuning of compression ratio and throughput

#### **Optimized Decompression**

- >2X throughput vs. zlib, equal to lzo

- Fully compatible with zlib and gzip archives

| Compressor name | Compression Throughput (MB/s) | Ratio |

|-----------------|-------------------------------|-------|

| lz4fast r131 -3 | 585                           | 50.51 |

| lz4 r131        | 518                           | 47.59 |

| isal 2.17.0     | 513                           | 41.35 |

| snappy 1.1.3    | 394                           | 47.83 |

| zlib 1.2.8 -1   | 82                            | 36.45 |

| Compressor name | Decompression Throughput (MB/s) | Ratio |

|-----------------|---------------------------------|-------|

| brotli 0.4.0 -0 | 318                             | 36.91 |

| isal 2.17.0     | 643                             | 41.35 |

| lz4 r131        | 2484                            | 47.59 |

| snappy 1.1.3    | 1335                            | 47.83 |

| zlib 1.2.8 -1   | 289                             | 36.45 |

| lzo1b 2.09 -1   | 671                             | 45.78 |

Preliminary Results generated with Izbench v1.2 via <a href="https://github.com/inikep/Izbench">https://github.com/inikep/Izbench</a> using Silesia Corpus on Intel® Xeon® E5-2650v3 (Haswell) CPU, turbo boost enabled, 16GB DDR4

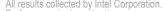

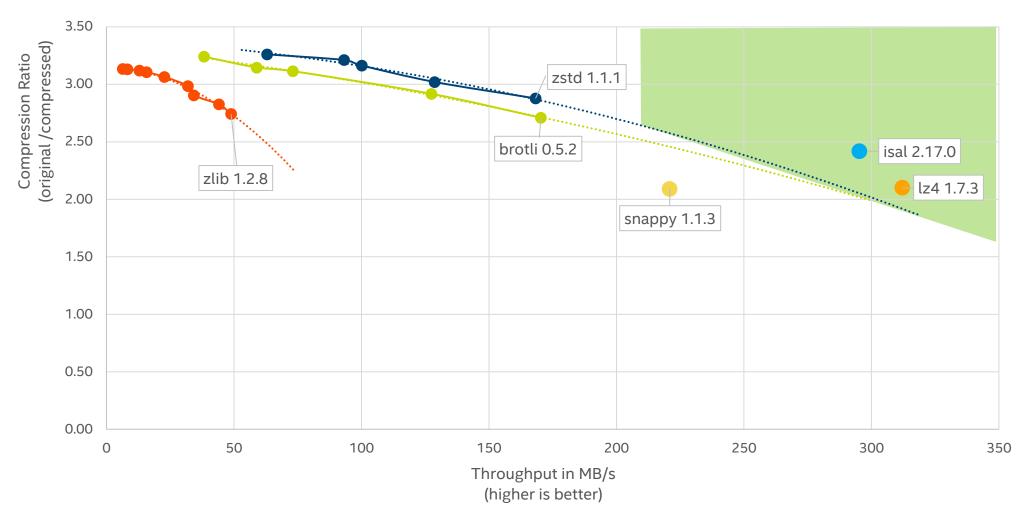

# Algorithms Comparison: Compression

#### **Compression Throughput vs. Compression Ratio**

# Algorithm Comparison: zlib, zstd, brotli...

**Compression Speed vs. Ratio - Silesia Corpus**

# Algorithms Comparison: Decompression

#### Decompression Throughput vs. Compression Ratio

#### Intel® Intelligent Storage Acceleration Library (ISA-L)

# Cycle/Byte Performance on the Intel® Xeon® Processor Scalable Fairing (cache cold cycle/byte)

|                                 | Intel® Xeon® Platinum 8180 Processor @ 2.5 GHz 1 Socket |                                                |                                                 |                   |  |  |  |

|---------------------------------|---------------------------------------------------------|------------------------------------------------|-------------------------------------------------|-------------------|--|--|--|

|                                 |                                                         | IS.                                            | ISA-L                                           |                   |  |  |  |

| ISA-L Function                  | C orpus                                                 | Cycle/Byte<br>Performance (lower is<br>better) | Single Core<br>Throughput (higher is<br>better) | Compression Ratio |  |  |  |

| Compress –<br>Stateless Level 0 | Calgary                                                 | 8.21                                           | 304 MB/s                                        | 40.52             |  |  |  |

| Compress –<br>Stateless level 0 | Silesia                                                 | 7.03                                           | 355 MB/s                                        | 41.35             |  |  |  |

| Compress –<br>Stateless Level 1 | Calgary                                                 | 8.54                                           | 292 MB/s                                        | 37.51             |  |  |  |

| Compress –<br>Stateless Level 1 | Silesia                                                 | 7.25                                           | 344 MB/s                                        | 36.86             |  |  |  |

| Compress –<br>Stateless Level 2 | -                                                       | -                                              | -                                               | -                 |  |  |  |

| Compress –<br>Stateless Level 3 | -                                                       | -                                              | -                                               | -                 |  |  |  |

| Decompress<br>"Inflate"         | Calgary                                                 | 6.23                                           | 400 MB/s                                        | N/A               |  |  |  |

| Decompress<br>"Inflate"         | Silesia                                                 | 5.30                                           | 471 MB/s                                        | N/A               |  |  |  |

| Cycle/Byte Performance | Single CoreThroughput |

|------------------------|-----------------------|

| (lower is better)      | (higher is better)    |

|                        |                       |

zlib 1.2.11 - Deflate

51.80 CC WT AVE ratio 39.24% 48 MB/s 49.29 Silesia WT AVE ratio 38.33% 50 MB/s

zlib 1.2.11 - Inflate

12.69 CC WT AVE 197 MB/s 12.25 Silesia WT AVE 204 MB/s

> \*\* ISA-L function uses AVX512 instructions

Il results collected by Intel Corporation

performance of that product when combined with other products. For more information go to

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, visit Intel Performance Benchmark Limitations (http://www.intel.com/performance/resources/benchmark\_limitations.htm).

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components,

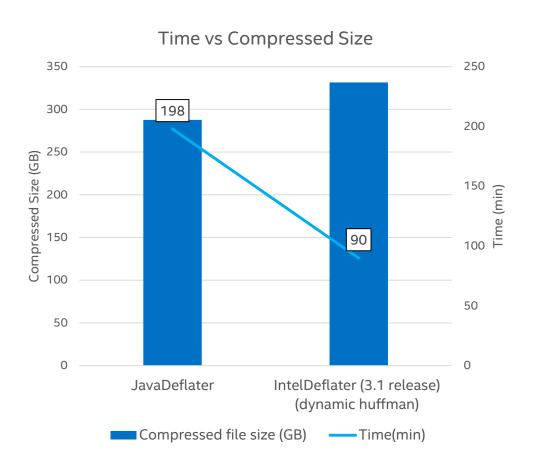

#### **Genomics Data**

- Huge volumes of data: 100s of GB is minimum

- Cancer Cloud: to come up with a cure, for each given cancer type, need 100k – 1M patients with 2TB of genomics per patient = 2 Exabytes per cancer

#### **Economics**

- Handling that volume is hard!

- DEFLATE does a great job on sequenced genomes

- Industry tools reliant on zlib, usually Java

#### **GATK Integration**

- Handling that volume is hard!

- DEFLATE does a great job on sequenced genomes

- Industry tools reliant on zlib, usually Java

Goal

After installing IGZIP, applications which use ZLIB for compression and decompression can use IGZIP for better performance without modification of your code.

Status

Under development.

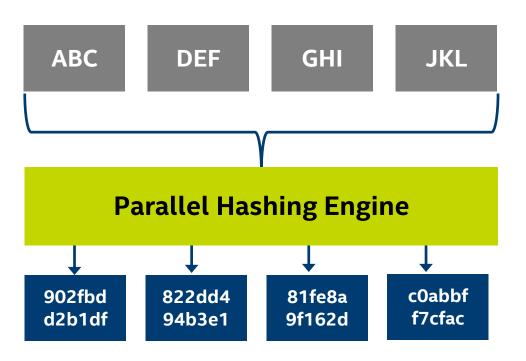

# **CRYPTOGRAPHIC HASHING**

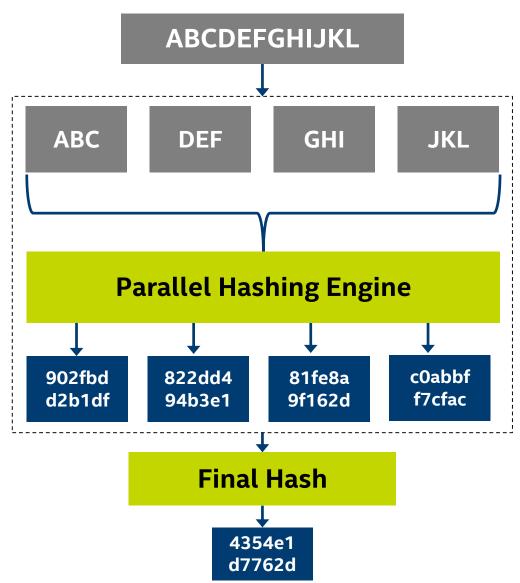

### Multibuffer Hash

#### **Vectorized hashes!**

- Uses Intel<sup>®</sup> Advanced Vector Extensions 512 (Intel<sup>®</sup> AVX-512)

- MD5, SHA1, SHA2-256, SHA2-512

- Asynchronous interface

- "Four for one"

#### Multihash

#### What is ISA-L Multihash?

- Synchronous interface

- SHA1 != SHA1

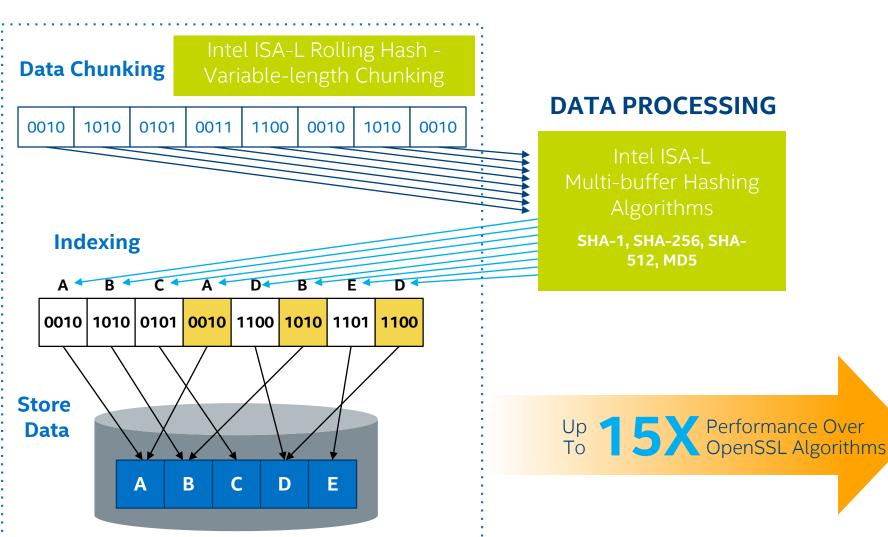

#### **Use Cases**

- Data integrity

- Encryption

- Deduplication

# Hashing Usage: Data Deduplication Optimi: (intel®)

#### **DEDUPLICATION ENGINE**

Intel ISA-L

3rdPartv

Key:

|                           | lı                                       | Intel® Xeon® Platinum 8180 Processor @ 2.5 GHz 1 Socket |                                          |                                                  |  |  |

|---------------------------|------------------------------------------|---------------------------------------------------------|------------------------------------------|--------------------------------------------------|--|--|

| ISA-L Function            | ISA-L                                    |                                                         | OpenSSL 1.0.2j                           |                                                  |  |  |

|                           | Cycle/Byte Performance (lower is better) | <b>Single Core Throughput</b> (higher is better)        | Cycle/Byte Performance (lower is better) | <b>Single Core Throughput</b> (higher is better) |  |  |

| Rolling Hash 32 bit       | 4.12                                     | 606 MB/s                                                | -                                        | -                                                |  |  |

| Rolling Hash 64 bit       | 2.53                                     | 988 MB/s                                                | -                                        | -                                                |  |  |

| Multihash SHA-1**         | 0.42                                     | 5.8 GB/s                                                | -                                        | -                                                |  |  |

| Multihash SHA-1 Murmur**  | 0.63                                     | 3.8 GB/s                                                | -                                        | -                                                |  |  |

| Multihash SHA-256**       | 0.82                                     | 2.9 GB/s                                                | -                                        | -                                                |  |  |

| Multibuffer SHA-1**       | Up 9X bandwidth boost 0.45               | 5.4 GB/s                                                | 4.13                                     | 605 MB/s                                         |  |  |

| Multibuffer SHA-256** Up  | 3X bandwidth 0.88                        | 2.7 GB/s                                                | 11.56                                    | 216 MB/s                                         |  |  |

| Multibuffer SHA-512**     | Up 7X bandwidth boost 1.08               | 2.2 GB/s                                                | 7.48                                     | 334 MB/s                                         |  |  |

| Multibuffer MD5**  Up 15) | bandwio h<br>boost 0.25                  | 9.7 GB/s                                                | 4.99                                     | 401 MB/s                                         |  |  |

\*\* ISA-L function uses AVX512 instructions

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or components as measured by those tests. Any difference in system hardware or software design or components they are considering purchasing. For more information on performance tests and on the performance performance Benchmark Limitations (http://www.intel.com/performance/resources/benchmark\_limitations.htm).

Software and worklands used in performance tests may have been ontimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components.

#### What is SHA\_NI:

The Intel® SHA Extensions are a family of seven Streaming SIMD Extensions (SSE) based instructions that are used together to accelerate the performance of processing SHA-1 and SHA-256 on Intel®Architecture processors.

- Update:

- sha1 ni x1 -> sha1 ni x2

- Sha256\_ni\_x1 -> sha256\_ni\_x2

- Supported platform: Denverton®, Skylake-Xeon®, to be continued...

- **Status:** Recently released and no official performance data yet.

| Instruction | Op 1     | Op 2            | Op 3                         | Opcode         |

|-------------|----------|-----------------|------------------------------|----------------|

|             | SHA      | 1 New Instructi | ions                         |                |

| SHA1RNDS4   | xmm (rw) | xmm/m128 (r)    | imm8                         | OF 3A CC /r ib |

| SHA1NEXTE   | xmm (rw) | xmm/m128 (r)    | NA                           | 0F 38 C8 /r    |

| SHA1MSG1    | xmm (rw) | xmm/m128 (r)    | NA                           | 0F 38 C9 /r    |

| SHA1MSG2    | xmm (rw) | xmm/m128 (r)    | NA                           | 0F 38 CA /r    |

|             | SHA2     | 56 New Instruc  | tions                        |                |

| SHA256RNDS2 | xmm (rw) | xmm/m128 (r)    | <xmm0><br/>(implicit)</xmm0> | 0F 38 CB /r    |

| SHA256MSG1  | xmm (rw) | xmm/m128 (r)    | NA                           | 0F 38 CC /r    |

| SHA256MSG2  | xmm (rw) | xmm/m128 (r)    | NA                           | 0F 38 CD /r    |

Table 1: Intel® SHA Extensions Definitions (rw - Read/Write, r - Read Only)

# STATE OF ISA-L

### Community of ISA-L

- Open Source Projects at Github:

- https://github.com/01org/isa-l

- https://github.com/01org/isa-1 crypto

- License: Algorithms are available under BSD license.

- To use it: see the included Getting Started Guide, API Guide, and C language reference applications

- Feedback & Notification

- Github Issues Report

- Subscribe to ISA-L: <a href="https://lists.01.org/mailman/listinfo/isal">https://lists.01.org/mailman/listinfo/isal</a>

# SUMMARIZE

# ☐ Features Update & Usercase Sharing

- Encryption

- Stitching CRC & copy

- CRC64

- Compression Level 3 supported

- Multi-buffer Hash sha\_ni

- ☐ State of the Project

# PERFORMANCE TABLE

|                          | Ir                                                 | Intel® Xeon® Platinum 8180 Processor @ 2.5 GHz 1 Socket |                                          |                                              |  |  |

|--------------------------|----------------------------------------------------|---------------------------------------------------------|------------------------------------------|----------------------------------------------|--|--|

| ISA-L Function           | ISA-L                                              |                                                         | OpenSSL 1.0.2j                           |                                              |  |  |

| ion in an endin          | <b>Cycle/Byte Performance</b><br>(lower is better) | <b>Single Core Throughput</b> (higher is better)        | Cycle/Byte Performance (lower is better) | Single Core Throughput<br>(higher is better) |  |  |

| Rolling Hash 32 bit      | 4.12                                               | 606 MB/s                                                | -                                        | -                                            |  |  |

| Rolling Hash 64 bit      | 2.53                                               | 988 MB/s                                                | -                                        | -                                            |  |  |

| Multihash SHA-1**        | 0.42                                               | 5.8 GB/s                                                | -                                        | -                                            |  |  |

| Multihash SHA-1 Murmur** | 0.63                                               | 3.8 GB/s                                                | -                                        | -                                            |  |  |

| Multihash SHA-256**      | 0.82                                               | 2.9 GB/s                                                | -                                        | -                                            |  |  |

| Multibuffer SHA-1**      | 0.45                                               | 5.4 GB/s                                                | 4.13                                     | 605 MB/s                                     |  |  |

| Multibuffer SHA-256**    | Jp 13X bandwidth boost 0.88                        | 2.7 GB/s                                                | 11.56                                    | 216 MB/s                                     |  |  |

| Multibuffer SHA-512**    | 1.08                                               | 2.2 GB/s                                                | 7.48                                     | 334 MB/s                                     |  |  |

| Multibuffer MD5**        | 5X bandwidth boost 0.25                            | 9.7 GB/s                                                | 4.99                                     | 401 MB/s                                     |  |  |

| AES-XTS 128              | 0.64                                               | 3.8 GB/s                                                | 0.64                                     | 3.8 GB/s                                     |  |  |

| AES-XTS 256              | 0.88                                               | 2.7 GB/s                                                | 0.89                                     | 2.7 GB/s                                     |  |  |

| AES-CBC 128 Decode       | 0.64                                               | 3.8 GB/s                                                | 0.64                                     | 3.8 GB/s                                     |  |  |

| AES-CBC 192 Decode       | 0.76                                               | 3.2 GB/s                                                | 0.76                                     | 3.2 GB/s                                     |  |  |

| AES-CBC 256 Decode       | 0.88                                               | 2.7 GB/s                                                | 0.88                                     | 2.7 GB/s                                     |  |  |

| AES-GCM 128              | 0.67                                               | 3.6 GB/s                                                | 1.58                                     | 1.5 GB/s                                     |  |  |

| AES-GCM 256              | 0.89                                               | 2.7 GB/s                                                | 1.83                                     | 1.3 GB/s                                     |  |  |

\*\* ISA-L function uses AVX512 instructions

All results collected by Intel Corporation

configuration may affect actual performance. Buyers should consult other solutions of the performance of systems and reliable the performance tests and reliable they are considering purchasing. For more information on performance tests and on the performance of Intel products, visit Intel Performance Benchmark Limitations (http://www.intel.com/performance/resources/benchmark\_limitations.htm).

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components,

|                          | In                                                                                                                                    | tel® Xeon® Platinum 8180 Proce                                     | ssor @ 2.5 GHz 1 Socket                                                      |                                                  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|

| ISA-L Function           | ISA-L                                                                                                                                 | ISA-L                                                              |                                                                              | L 1.0.2j                                         |

| ion 2 i unenon           | <b>Cycle/Byte Performance</b> (lower is better)                                                                                       | <b>Single Core Throughput</b><br>(higher is better)                | <b>Cycle/Byte Performance</b> (lower is better)                              | <b>Single Core Throughput</b> (higher is better) |

| PQ Gen (16+2)**          | 0.10                                                                                                                                  | 23.4 GB/s                                                          | -                                                                            | -                                                |

| XOR Gen (16+1)**         | 0.10                                                                                                                                  | 24.2 GB/s                                                          | -                                                                            | -                                                |

| Reed Solomon EC (10+4)** | 0.19                                                                                                                                  | 12.7 GB/s                                                          | -                                                                            | -                                                |

| CRC16 T10                | 0.22                                                                                                                                  | 11.0 GB/s                                                          | -                                                                            | -                                                |

| CRC32 IEEE (802.3)       | 0.22                                                                                                                                  | 11.1 GB/s                                                          | -                                                                            | -                                                |

| CRC32 iSCSI              | 0.18                                                                                                                                  | 13.8 GB/s                                                          | -                                                                            | -                                                |

| CRC32 GZIP Reflective    | 0.24                                                                                                                                  | 10.3 GB/s                                                          | -                                                                            | -                                                |

| CRC64 Normal             | 0.22                                                                                                                                  | 11.0 GB/s                                                          | Cyclo/Pyto Porformanco                                                       | Single CoreThroughput                            |

| CRC64 Reflective         | 0.19                                                                                                                                  | 12.9 GB/s                                                          | - Cycle/Byte Performance<br>(lower is better)                                | Single CoreThroughput<br>(higher is better)      |

| Compress - Stateless     | Level 0 8.21 CC WT AVE ratio 40.52 7.03 Silesia WT AVE ratio 41.35 Level 1 8.54 CC WT AVE ratio 37.51 7.25 Silesia WT AVE ratio 36.86 | Level 0<br>304 MB/s<br>355 MB/s<br>Level 1<br>292 MB/s<br>344 MB/s | 51.80 CC WT AVE ratio 39.24<br>49.29 Silesia WT AVE ratio 38.3<br>zlib 1.2.1 | 33% 50 MB/s<br><b>1 - Inflate</b>                |

| Decompress "Inflate"     | 6.23 CC WT AVE<br>5.30 Silesia WT AVE                                                                                                 | 400 MB/s<br>471 MB/s                                               | 12.69 CC WT AVE<br>12.25 Silesia WT AVE                                      | 197 MB/s<br>204 MB/s                             |

\*\* ISA-L function uses AVX512 instructions

All results collected by Intel Corporation

enformance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of mice products as measured by those tests. Any difference in system randware of solid consult of the sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the efformance of Intel products, visit Intel Performance Benchmark Limitations (http://www.intel.com/performance/resources/benchmark\_limitations.htm).

oftware and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components,

|                     | lı .                                                                                                                                  | ntel® Xeon® Platinum 8180 Proc                                     | essor @ 2.5 GHz 1 Socket                                             |                                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------|

| ISA-L Function      | ISA-L                                                                                                                                 |                                                                    | zlib 1.2                                                             | .11                                         |

| ISA-ET unction      | <b>Cycle/Byte Performance</b> (lower is better)                                                                                       | <b>Single Core Throughput</b> (higher is better)                   |                                                                      |                                             |

| ompress - Stateless | Level 0 8.21 CC WT AVE ratio 40.52 7.03 Silesia WT AVE ratio 41.35 Level 1 8.54 CC WT AVE ratio 37.51 7.25 Silesia WT AVE ratio 36.86 | Level 0<br>304 MB/s<br>355 MB/s<br>Level 1<br>292 MB/s<br>344 MB/s | 51.80 CC WT AVE ratio 39.24%<br>49.29 Silesia WT AVE ratio<br>38.33% |                                             |

| ecompress "Inflate" | 6.23 CC WT AVE<br>5.30 Silesia WT AVE                                                                                                 | 400 MB/s<br>471 MB/s                                               |                                                                      |                                             |

|                     |                                                                                                                                       |                                                                    | Cycle/Byte Performance<br>(lower is better)                          | Single CoreThroughput<br>(higher is better) |

|                     |                                                                                                                                       |                                                                    | zlib 1.2.11                                                          | - Deflate                                   |

|                     |                                                                                                                                       |                                                                    | 51.80 CC WT AVE ratio 39.24<br>49.29 Silesia WT AVE ratio 38.3       | % 48 MB/s<br>3% 50 MB/s                     |

|                     |                                                                                                                                       |                                                                    | zlib 1.2.1                                                           | I - Inflate                                 |

|                     |                                                                                                                                       |                                                                    | 12.69 CC WT AVE<br>12.25 Silesia WT AVE                              | 197 MB/s<br>204 MB/s                        |

|                     |                                                                                                                                       |                                                                    |                                                                      | A-L function uses<br>/X512 instructions     |

(intel)